## Essential EMC Training for Design Engineers

Dr. Min Zhang

# Our approach

## Training Programme Pyramid Structure MACHOOC Expertise Propels Excellence

Filter Design

**SMPS & Motors**

**PCB** Design

Digital & Analog

Design

High frequency measurement & troubleshooting

TOP Level

Filtering (Ferrite)

Shielding

Grounding

Cables & Connectors

Medium Level

**Module 1**

Module 3

Fundamental

Module 4

# Design for EMC Course Objectives - 3 day MACHO Course Sexual Design for EMC Course Objectives - 3 day

- Introduction to EMI, EMC & SIPI

- The purpose of this course introducing the first principles and the tools

- Understand EMC design principles for PCB level; grounds, trace coupling, multi-layer PCB

- Understand EMC design principles for cables and connections

- Understand EMC design principles for shielding

- Understand EMC design principles for filtering

- Understand EMC design techniques for switched converters

- Understand EMC design principles for digital and analogue circuits

# High-Frequency Measurement and Troubleshooting Course Objectives - 2 day

THE PARTY AND ADDRESS OF THE PARTY AND ADDRESS

- Understand the first principles of high-frequency measurement.

- Avoid pitfalls of high-frequency high-speed measurement.

- Understand direct contact measurement techniques and circuit capacitive loading phenomena.

- Understand magnetic-field loops, theory, and applications.

- Learn how to use RF current probes, theory, and applications, including advanced usages.

- Master advanced troubleshooting techniques, including locating resonance structures and ESD troubleshooting.

# Sample Pages

## Fundamentals - Module 1

Suited for engineers of all levels, including mechanical engineers, system engineers and junior-level engineers.

With questions designed to help engineers understand the concepts introduced in this sector. See an example on the next slide.

- The Decibel (dB) & using the dB

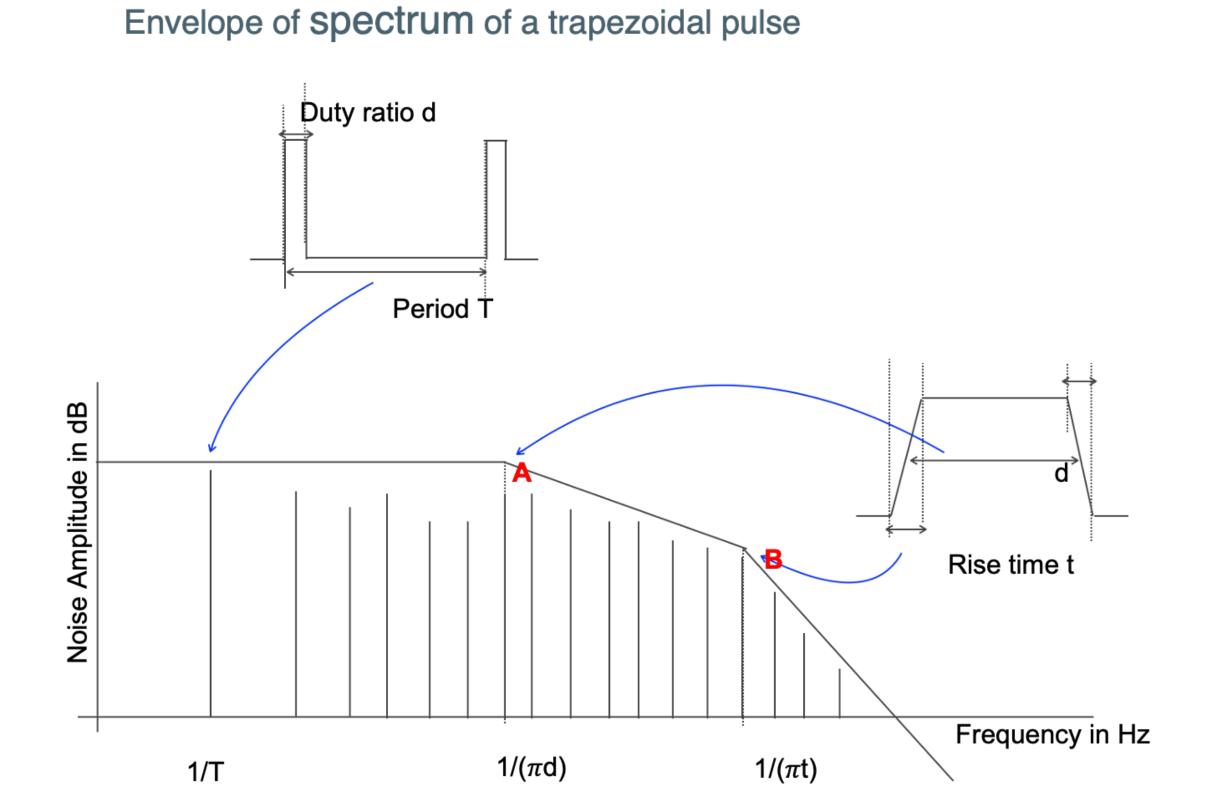

- Time versus Frequency: Trapezoidal Wave

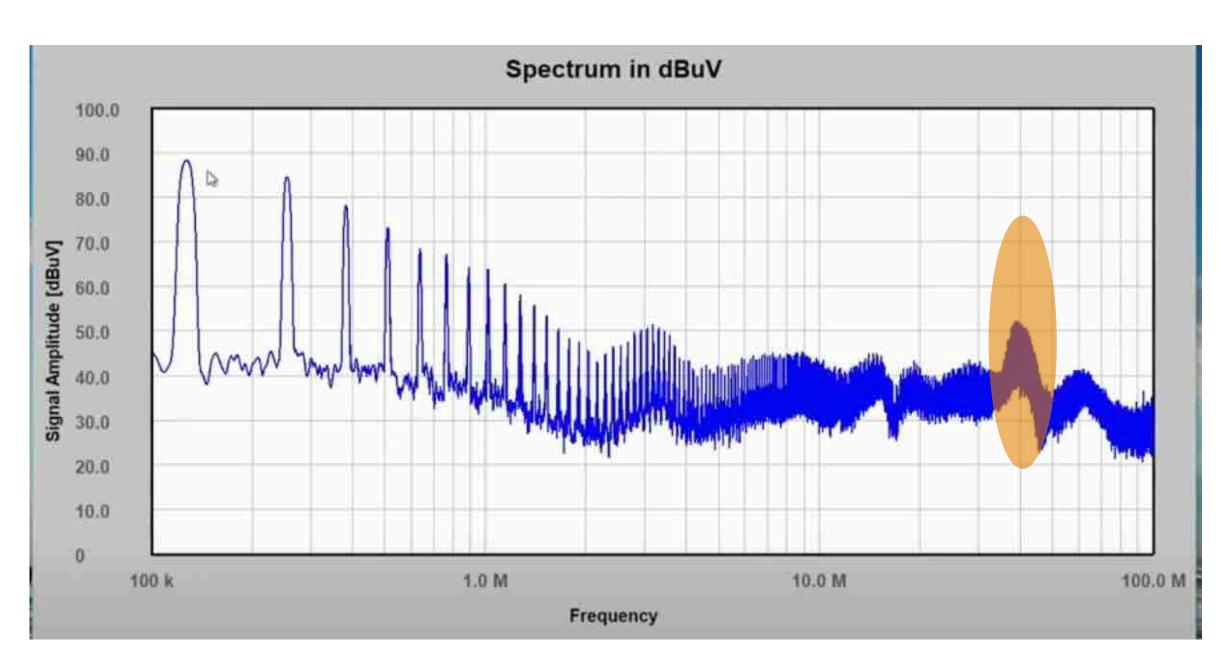

- Broadband and Narrowband Noise

- Time vs Frequency Analysis

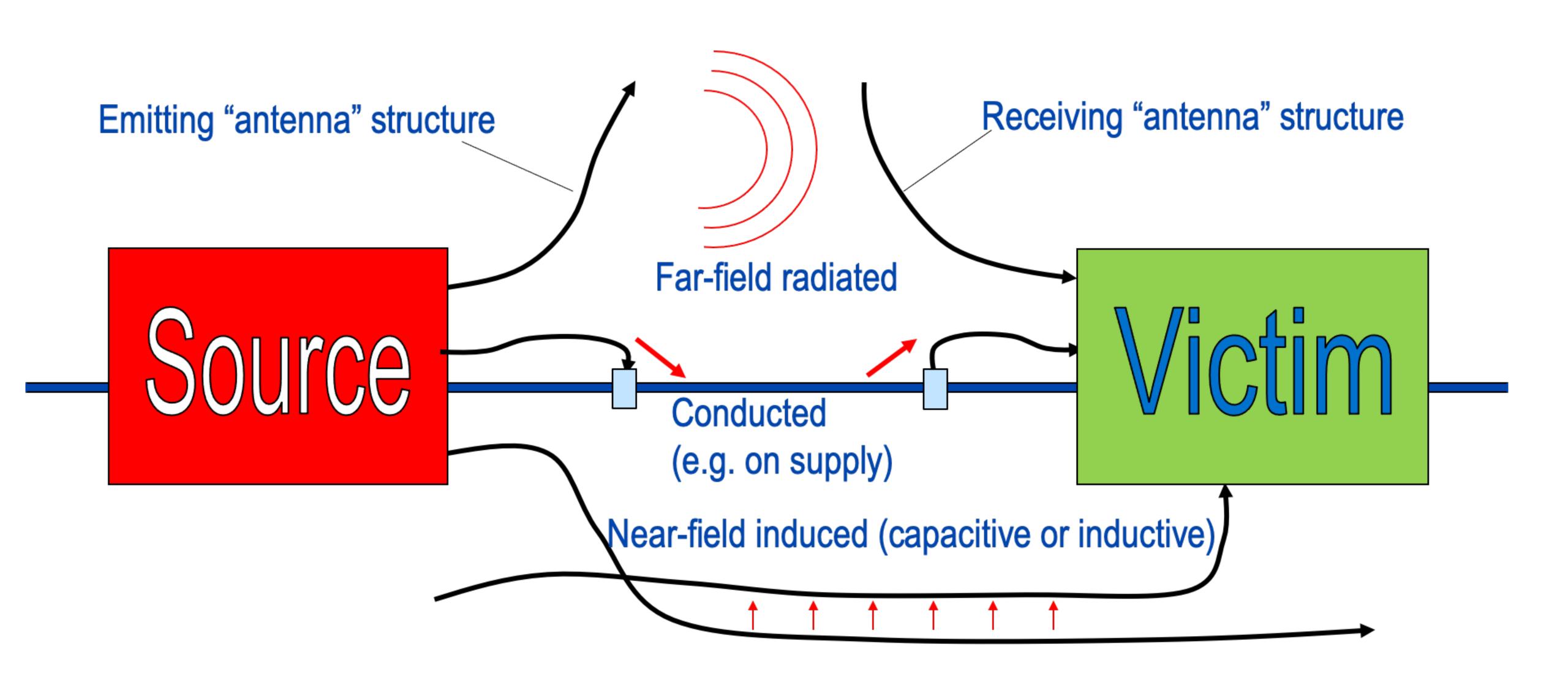

- Coupling Mechanisms

- Near and far fields

- Understanding Parasitics

# Coupling Mechanisms

## Time vs Frequency Domain

# Coupling

5 mil wide/5 mil space H = 4 milsH = 10 milsH = w + s + w = 15 mils

Crosstalk, unwanted signals on other lines unintendedly - SIPI Interference - EMC

Common mode coupling path - EMC

Even true differential signal pairs use a common return path. It is *NOT* true that the return current of one signal line is carried by another line. - it depends

Source: What every PCB Designer Should know - Return Current Path (with Eric Bogatin) <a href="https://www.youtube.com/watch?">https://www.youtube.com/watch?</a> v=icRzEZF3eZo

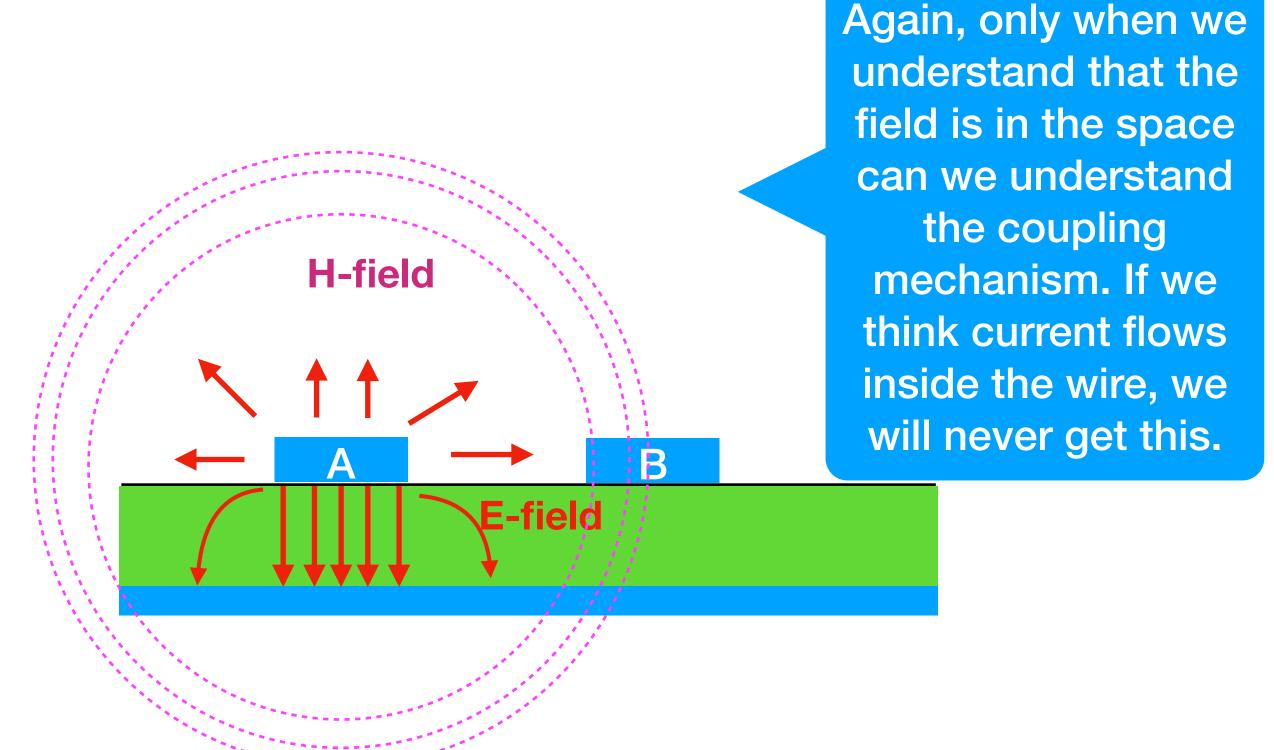

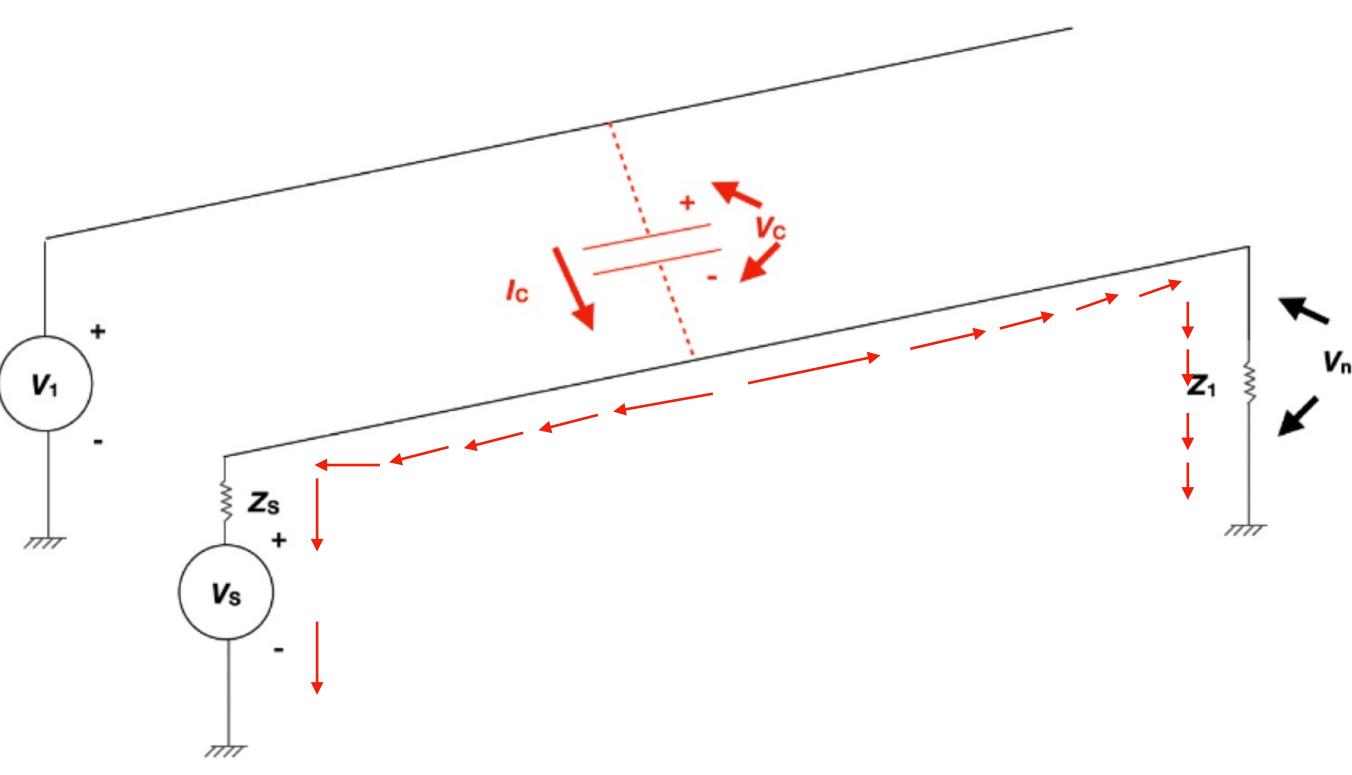

### Capacitive Coupling - E-field Coupling MACHO

- Two conductors represent two parallel run wires, traces over a PCB, etc.

- Ignoring the inductance effect in this

- represents the noise source.

- What is the induced interference voltage on  $Z_{l}$ ?

$$V_n = C \frac{dV_1}{dt} (Z_S \mid \mid Z_l)$$

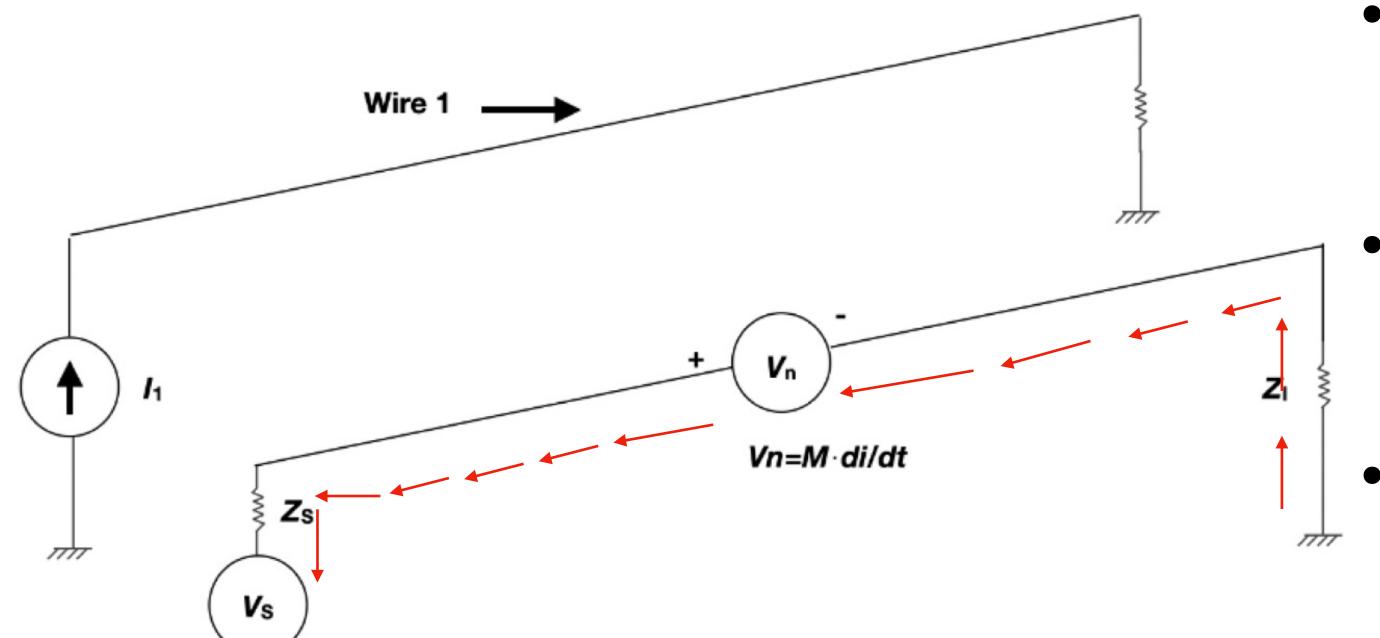

## Inductive Coupling - H-field Coupling MACHOOC

- Two conductors represent two parallel run wires, traces over a PCB, etc.

- Ignoring the inductance effect in this example.

- I1 represents the noise source, in this case, it is a current source.

- What is the induced interference voltage on  $Z_1$ ?

$$V_l = M \frac{dI_1}{dt} \frac{Z_l}{Z_S + Z_l}$$

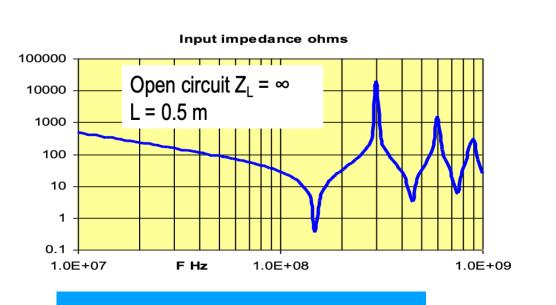

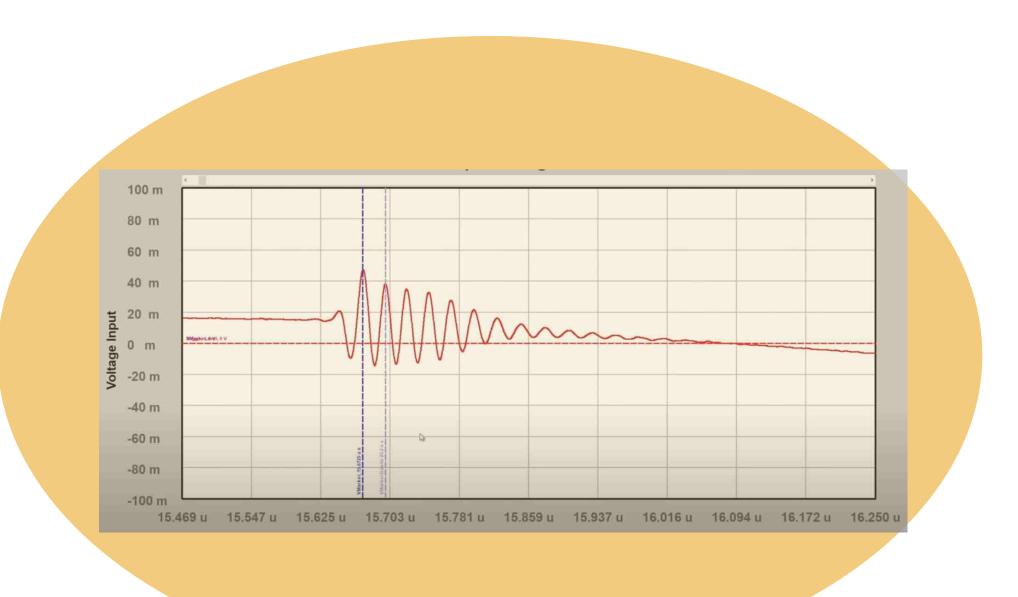

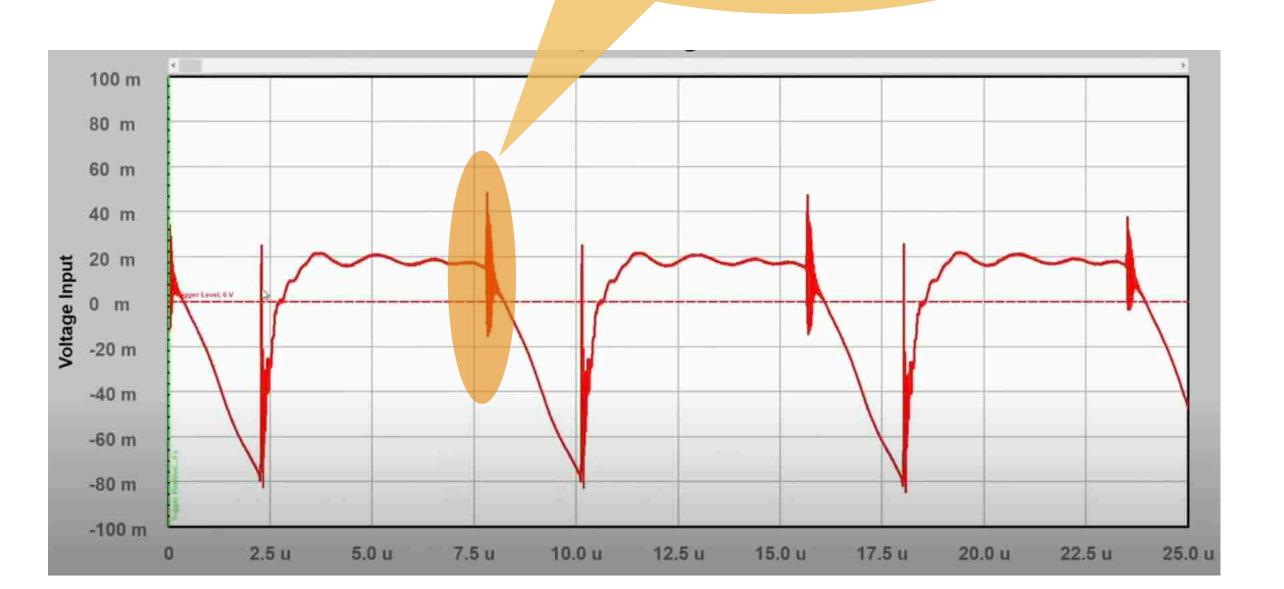

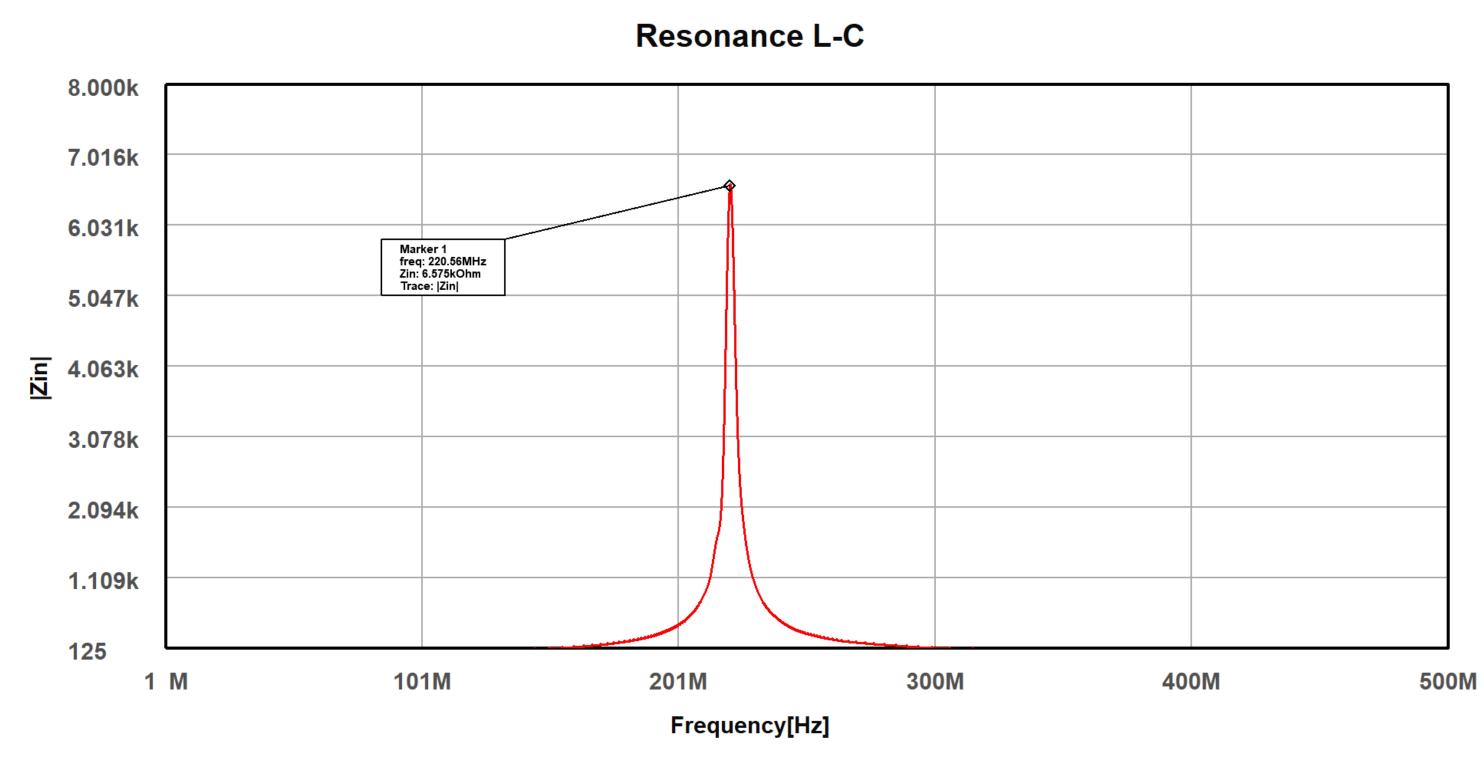

## Resonance Circuits

The impedance curve of an L-C resonant circuit

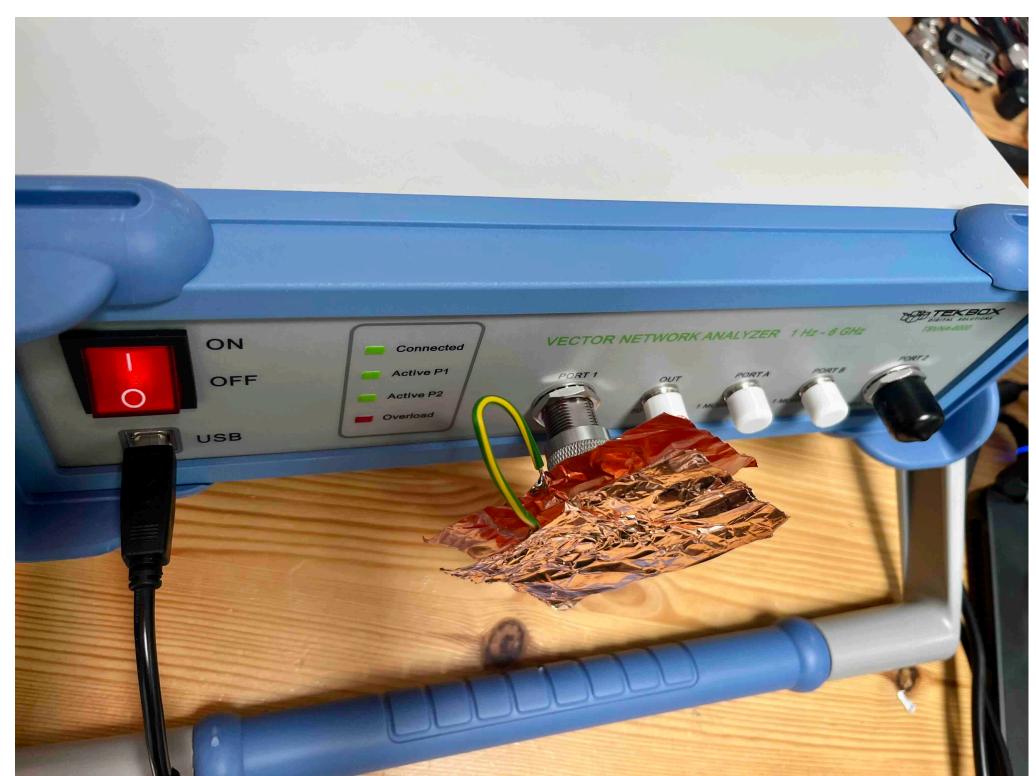

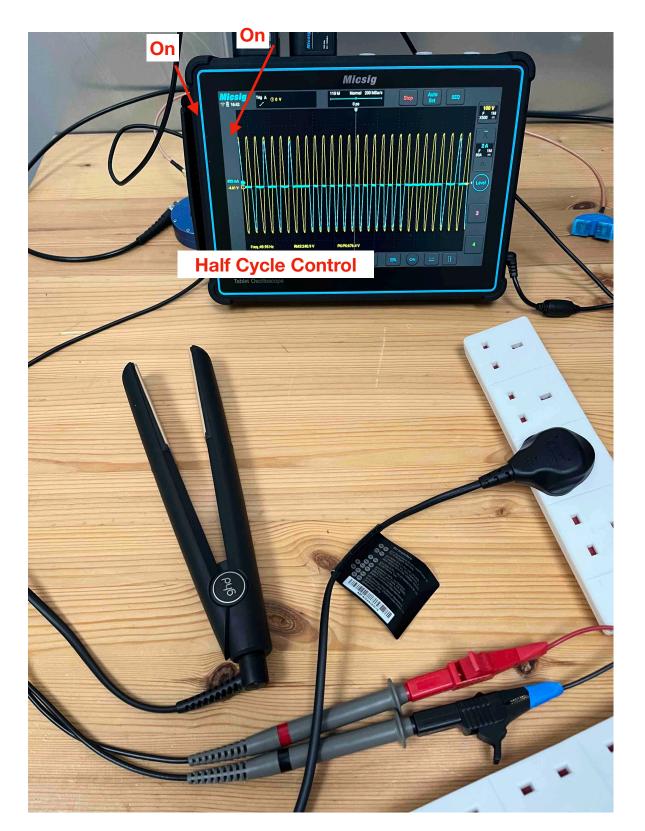

# Issues with a resonance structure propels excellence

Cursors

AX: 1.45 ns

AY: 866.6mV

BX: 6.05 ns

BY: -933.3mV

ΔX: 4.6ns

ΔY: -1.8V

1/ΔX: 217.3MHz

VRM51 Vpp1 RiseTime1 Freq1

1.0284V 7.9184V 1.0000ns

1 1.000 ns

1 1.000 ns

1 1.00mV

0 -80.0mV

2 1.00mV

0 0.00V

3 1.00mV

0 0.00V

Resonance

Demonstration from an immunity point of view

## Question 1

Interference between an AM car radio and an overhead power line is likely due to

- A.Conducted coupling

- B.E-field coupling

- C.Magnetic field coupling

- D.Radiation coupling

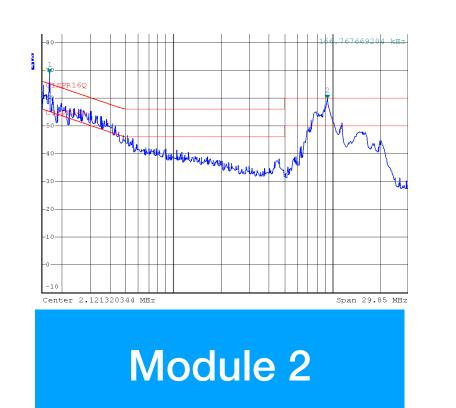

## Fundamentals - Module 2

Suited for advanced level design engineers.

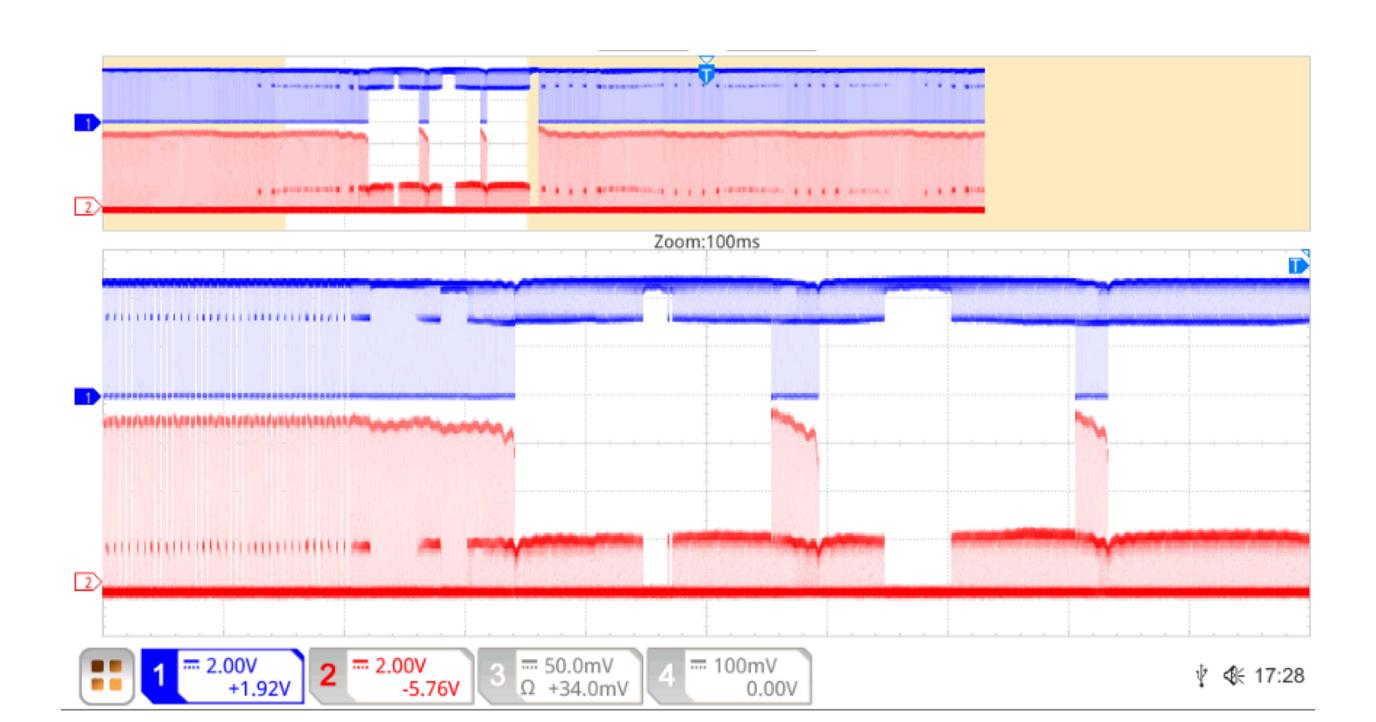

Seeing is believing; with time-domain demonstrations, engineers will grasp the concepts introduced in this module. Real-life case studies also help engineers to understand the EMC tests better.

- Low vs. High Frequency with a Demonstration Reinforcing the Concept of Loop Area and Inductance

- Differential Versus Common-Mode Noise with a Demonstration -Understanding Common-Mode Noise Is Essential for Solving EMI Issues

- Resonance Structure

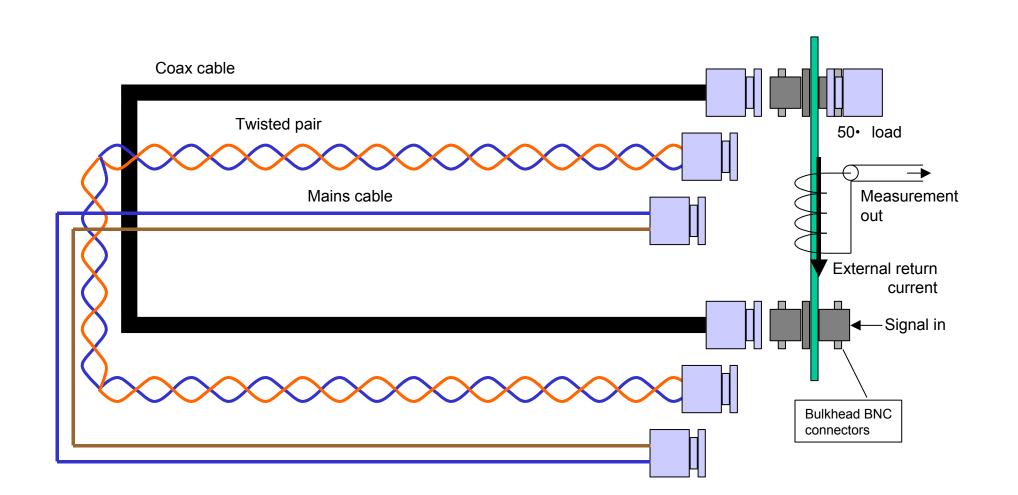

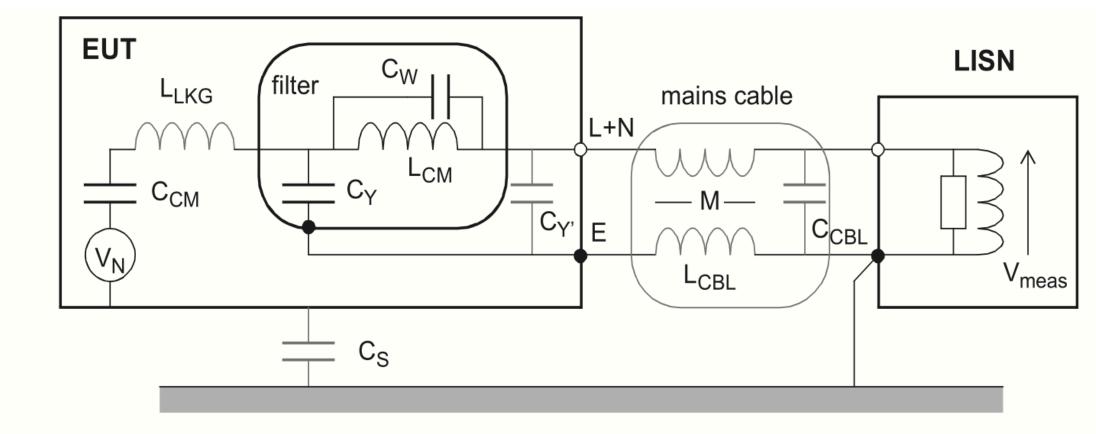

- The Science Behind EMC Tests (A Walkthrough of Common EMC Tests) -Engineers Should Understand the Why and How of EMC Tests Before They Begin Designing a Compliance Product

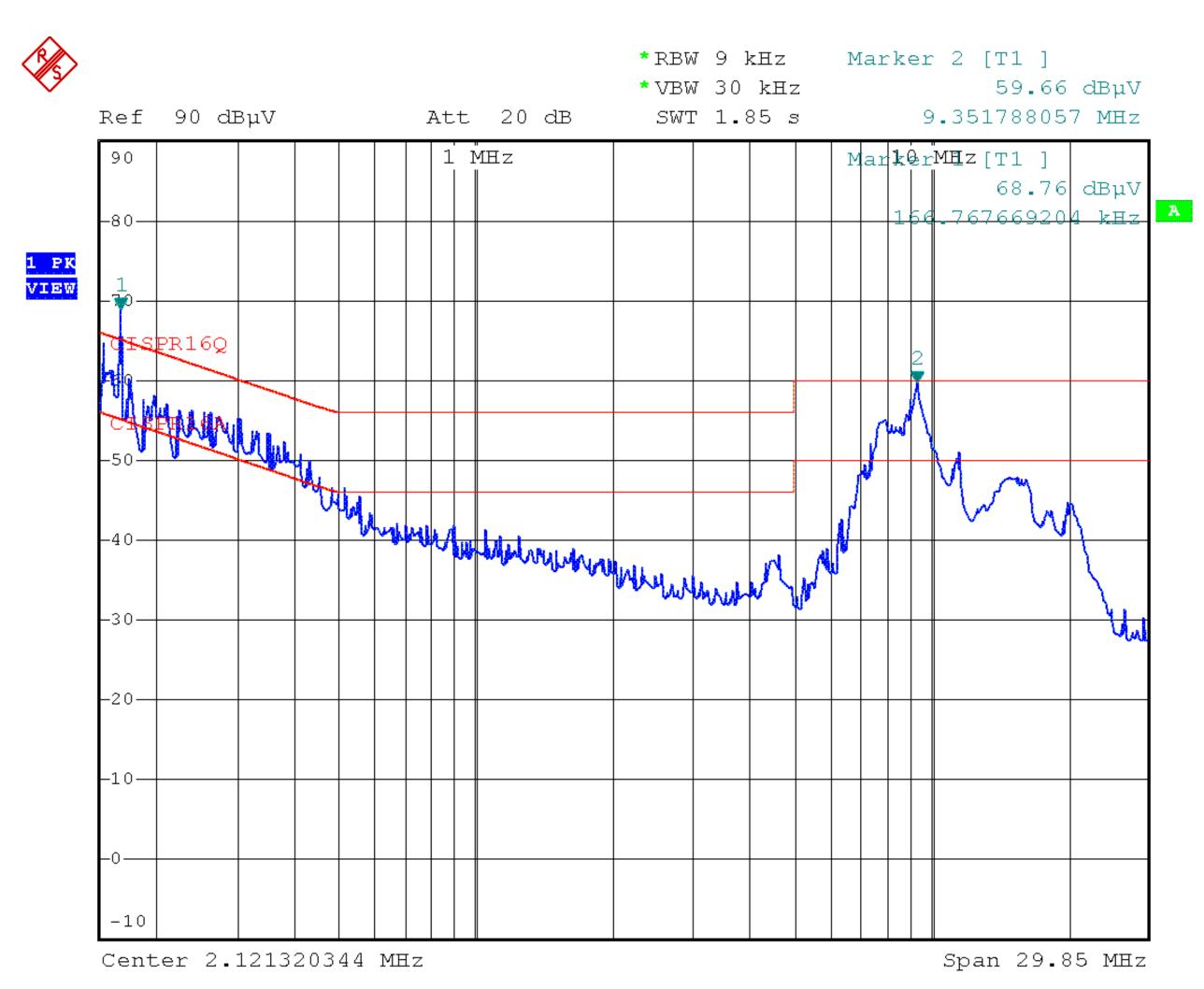

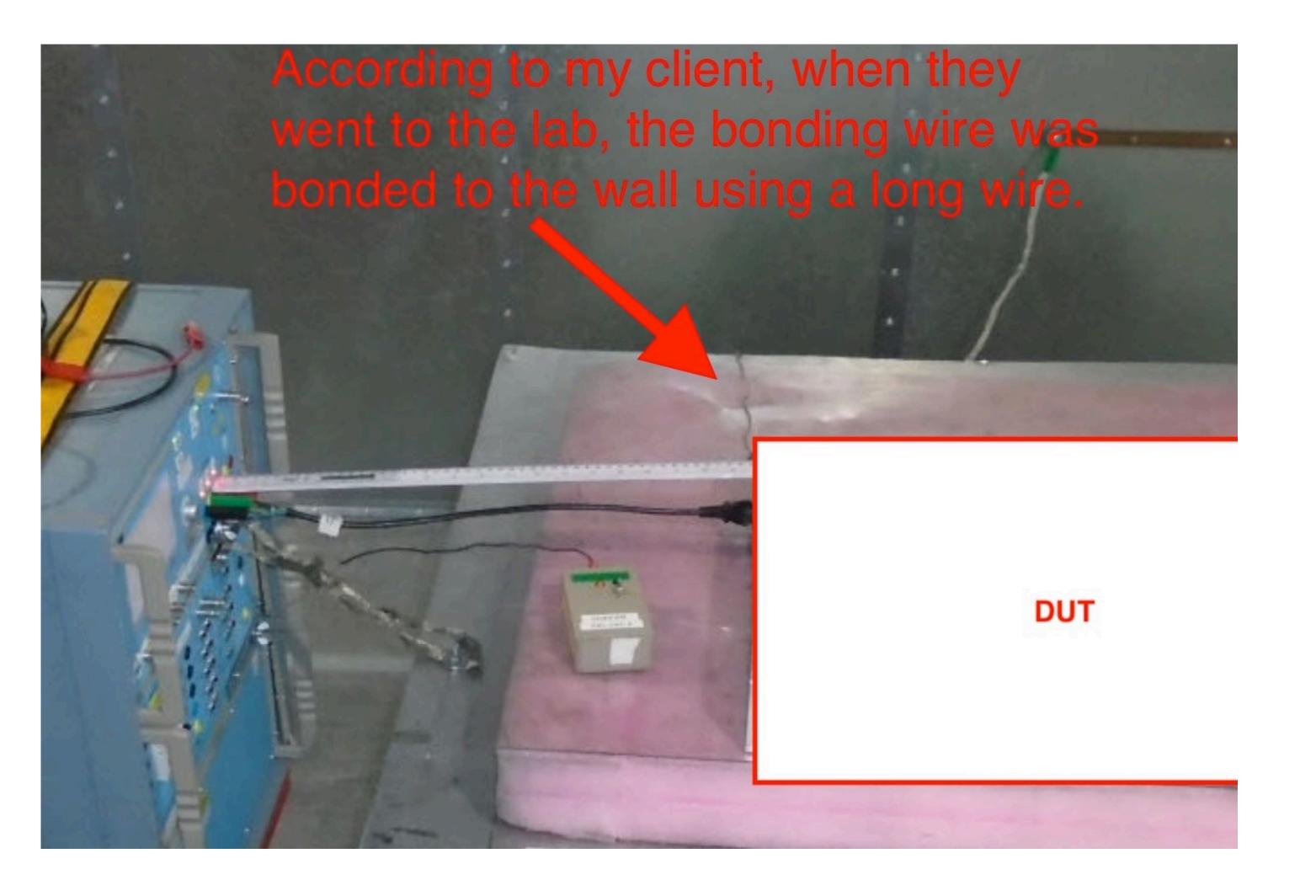

- Pitfalls of EMC Tests through Real Life Case Studies

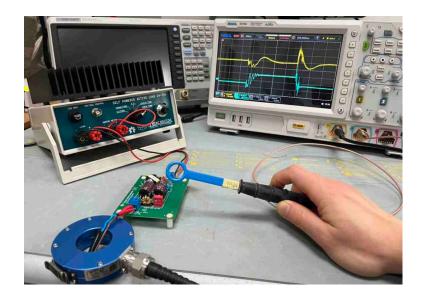

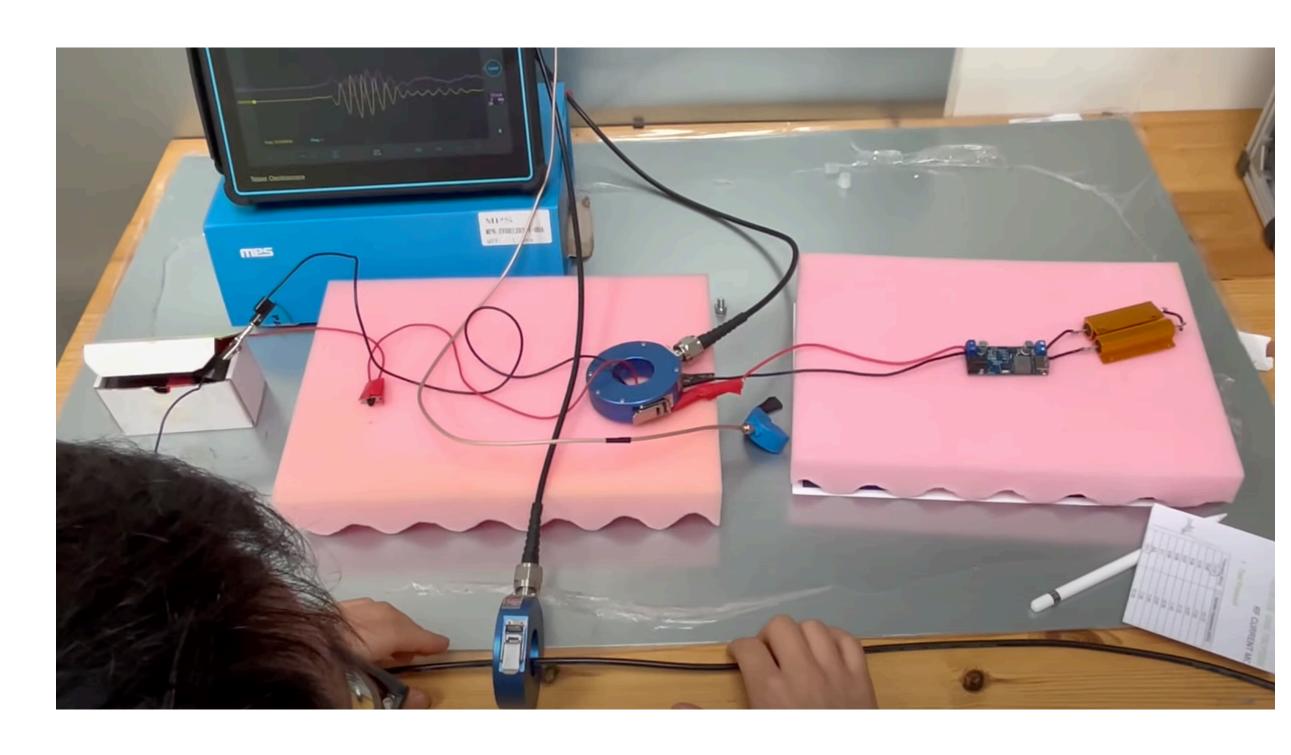

## Demonstrations

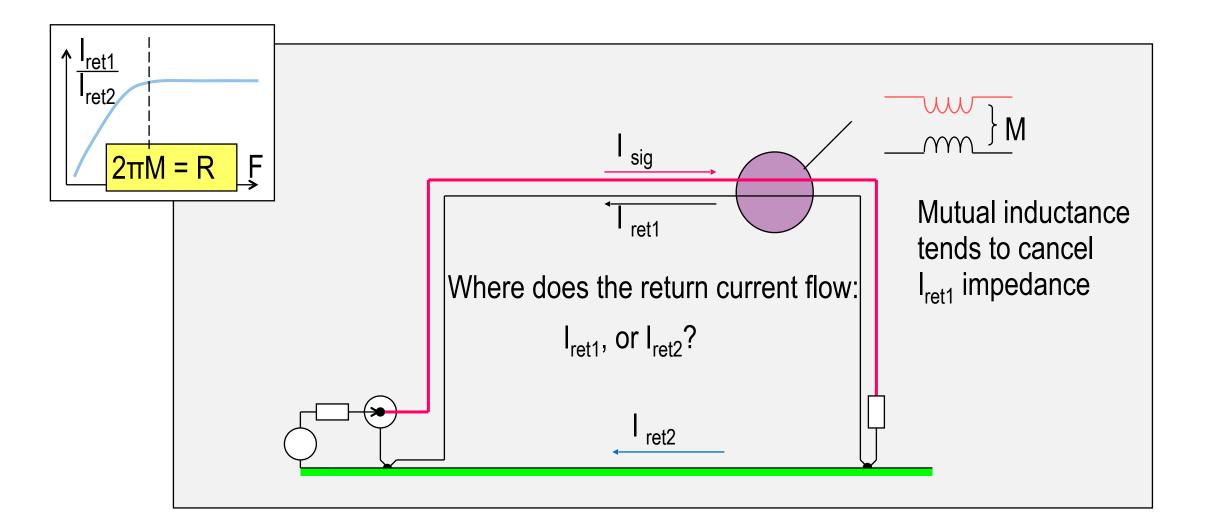

#### The ground return path demo

#### DM vs CM demo

## A Walkthrough of EMC Tests

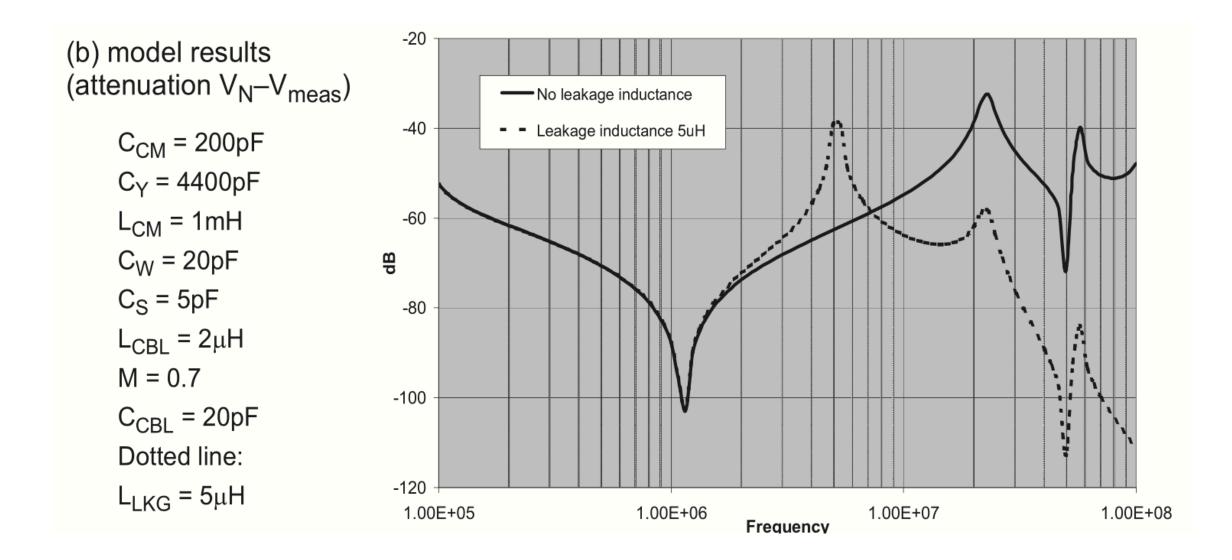

(a) equivalent circuit in common mode

# Case Study 1

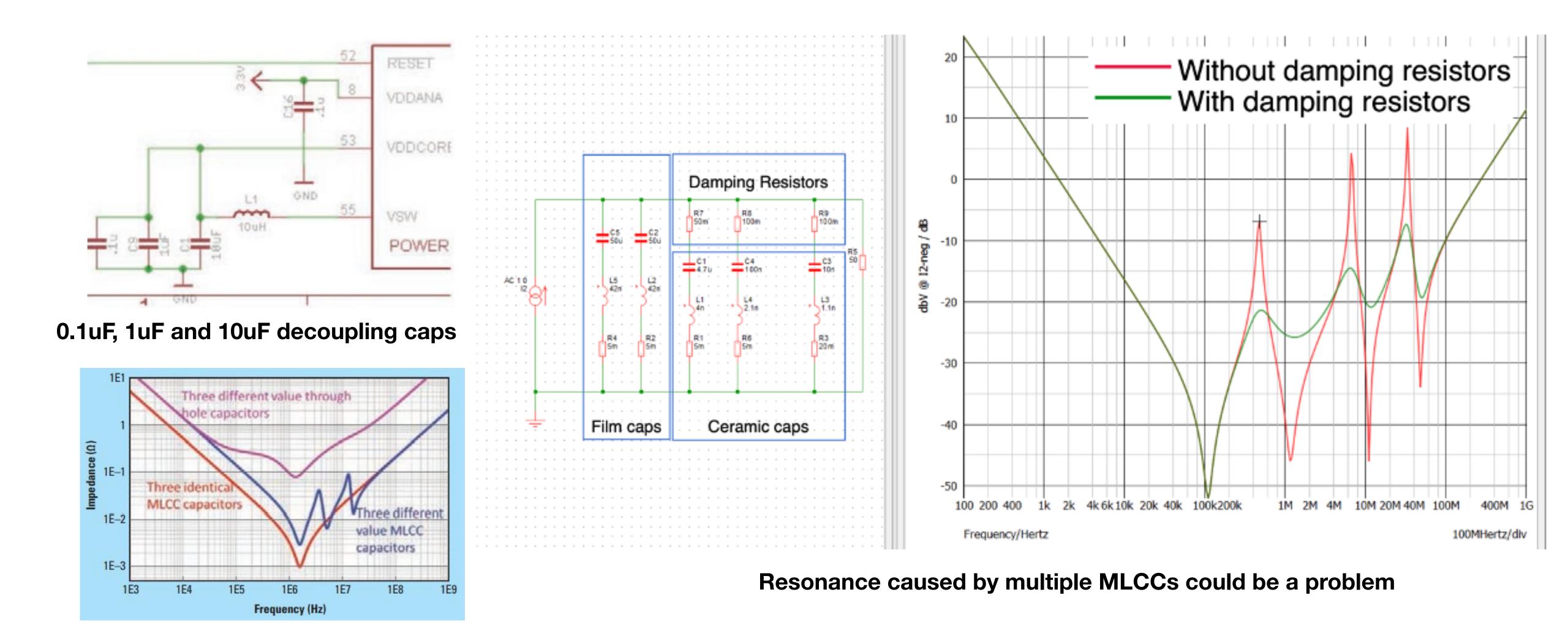

### The Myth of Three Capacitor Values

Three capacitor values all the same large value may provide lower impedance across the spectrum than three different value capacitors (and without the parallel resonant peaks at intermediate frequencies), but this does not mean it is a more robust solution.

Source: https://www.signalintegrityjournal.com/articles/1589-the-myth-of-three-capacitor-values

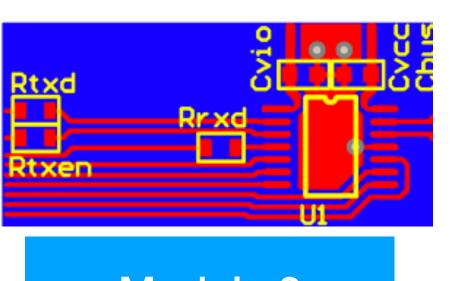

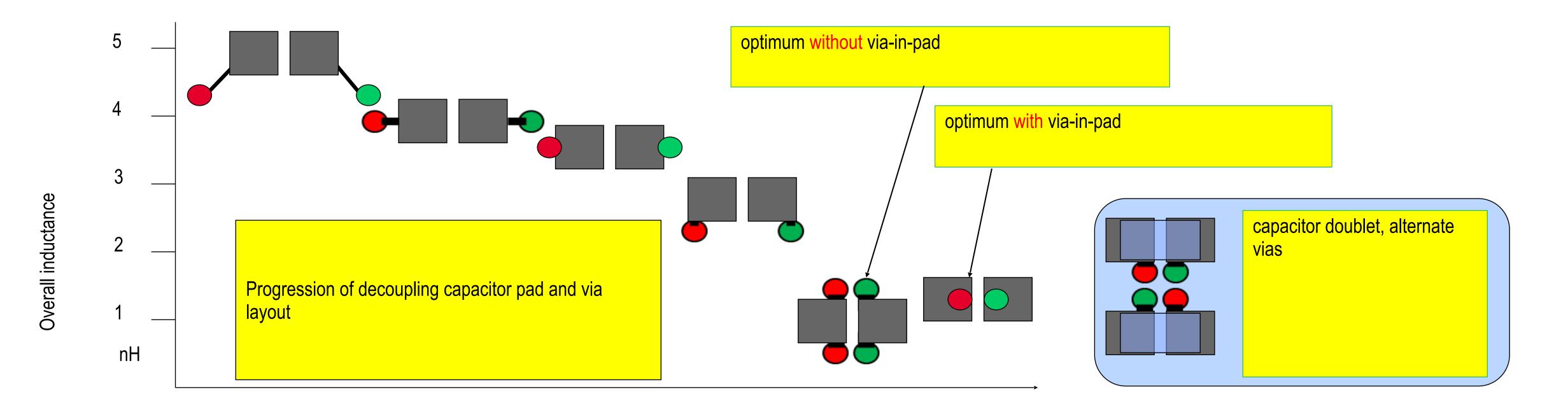

# SMD capacitor layout

- The positioning of vias to power planes relative to SM pads affects the overall inductance of each instance of decoupling capacitor

- -lowest inductance is achieved with the + and vias very close together (to benefit from mutual coupling)

# Analog Susceptibility